在2025年IEEE国际互连技术大会(IITC)上,比利时微电子研究中心(IMEC)向全球半导体行业展示了其最新的16纳米间距钌(Ru)互连技术突破。这项具有里程碑意义的研究成果标志着芯片制造技术向更小尺寸、更高性能方向迈出了关键一步。

IMEC研发团队采用创新的半镶嵌集成工艺,成功实现了平均电阻仅为656Ω/µm的16纳米间距钌互连结构。这项技术突破主要解决了当金属间距缩小至20纳米以下时,传统铜互连工艺面临的电阻-电容(RC)延迟加剧的行业难题。项目总监Seongho Park表示:"我们的研究为A7及更先进制程节点的互连技术提供了可行的解决方案。"

该技术的核心创新在于三个关键工艺突破:首先,研发团队采用了改进版的基于极紫外光刻(EUV)的自对准双重图案化(SADP)技术,实现了更精细的图形定义;其次,优化了图案反转步骤与二氧化硅间隙填充工艺的组合;第三,开发了新型钌蚀刻工艺,显著降低了线桥缺陷的产生率。

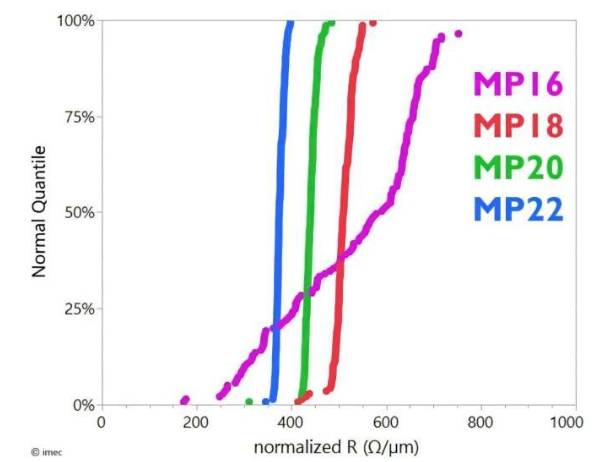

实验数据显示,在16纳米间距下,40%的测试结构达到了预设电阻目标,相当于8纳米宽的局部互连性能。更令人振奋的是,在18-22纳米间距范围内,全晶圆良率稳定保持在90%以上,展现出优异的工艺稳定性。Park补充道:"我们正在开发完全自对准通孔(FSAV)技术,这将为双金属层集成方案奠定基础。"

IMEC的研究还展示了外延生长的25纳米钌薄膜,其电阻率已接近块体材料水平,这为未来互连技术的进一步发展指明了方向。相比传统铜互连技术,这种钌半镶嵌工艺在20纳米以下间距展现出明显的性能优势,不仅解决了RC延迟问题,还能提供约11%的互连密度提升。

这项研究成果是IMEC长期技术积累的体现。早在2022年,该机构就曾展示过18纳米间距钌线的可行性。如今的技术突破不仅将互连密度推向新高度,更为半导体行业应对未来制程微缩挑战提供了重要技术储备。

更多信息: Gilles Delie 等人,利用 SiN 基核心实现 Ru 半镶嵌工艺中的 MP16/18 集成,以实现间隔层为电介质的SADP。