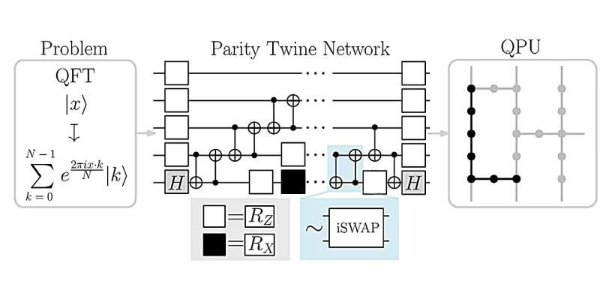

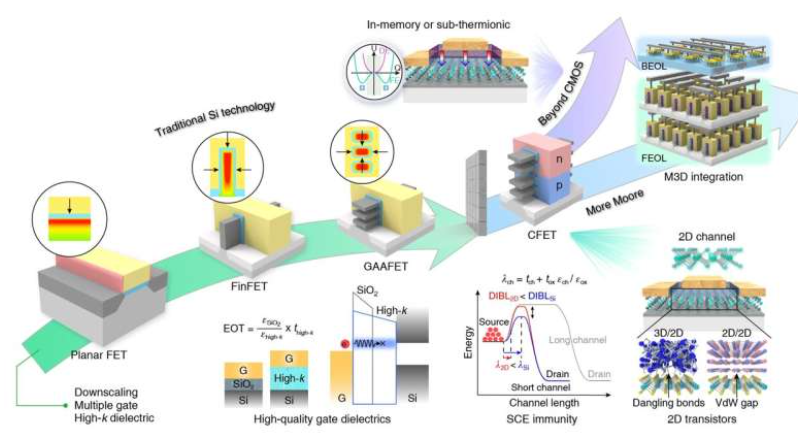

首尔国立大学工程学院宣布,由电气与计算机工程系李哲浩教授带领的研究团队,已制定了“栅极堆叠”工程的全面路线图。作为二维(2D)晶体管核心技术,“栅极堆叠”工程正成为下一代半导体器件的关注焦点,相关研究已发表于《自然电子学》杂志。

当前,多数半导体依赖硅基CMOS技术,但随着技术进入亚纳米领域,物理和静电限制日益凸显。二维半导体因其在原子厚度下仍能保持电学特性,被视为超越硅的沟道材料,吸引了包括三星、台积电等在内的全球领先半导体公司的关注,并已被纳入后硅时代技术路线图。然而,二维半导体商业化面临的最大挑战是栅极堆叠集成技术,其质量直接影响器件性能和稳定性。

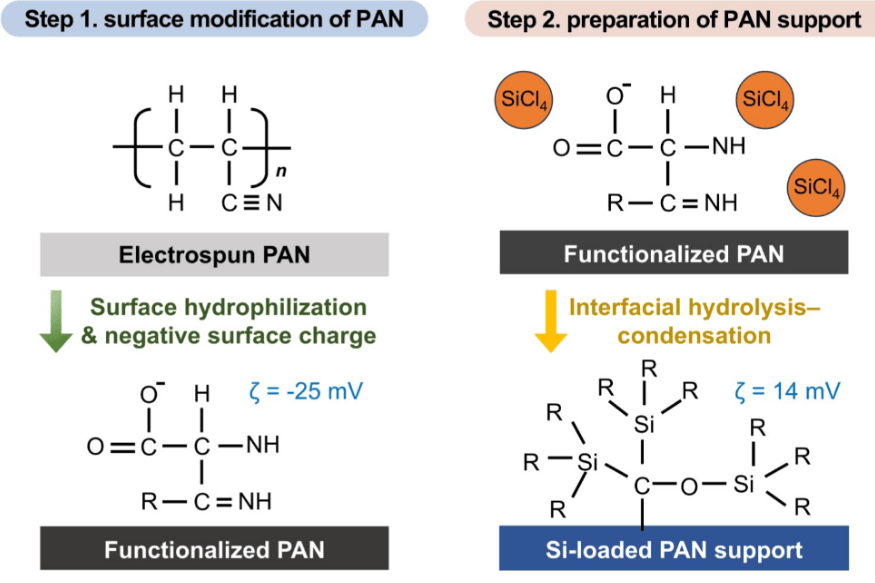

李哲浩教授团队分析了多种栅极堆叠集成方法,并根据界面陷阱密度、等效氧化层厚度等性能指标进行了定量基准测试。研究将栅极堆叠集成方法细分为五类,并与国际器件与系统路线图(IRDS)目标对比,形成了系统性的发展路线图。此外,研究还展示了铁电材料栅极堆叠技术在下一代器件中的应用潜力,并强调了实际工业应用的可行性,包括后段工艺(BEOL)兼容性、低温沉积等要求。

这项研究不仅为下一代半导体发展提供了蓝图,还证实了超低功耗、高性能晶体管的可行性,并提出了单片三维集成和BEOL兼容工艺的具体技术方向。李教授表示:“高质量栅极堆叠的实现是二维晶体管商业化的关键。这项研究提出了克服挑战的标准蓝图,对学术界和工业界都具有重大影响。”

更多信息: Yeon Ho Kim 等,二维晶体管的栅极堆叠工程,《自然电子学》(2025)。期刊信息:《自然电子学》