韩国大邱庆北科学技术院(DGIST)电气工程与计算机科学系的Jae Eun Jang教授与Goeun Pyo博士团队成功开发出“双重调制垂直堆叠晶体管”。这种晶体管能在二维纳米级沟道结构中稳定工作,有效消除电流泄漏问题。相关研究成果已发表在《Advanced Science》期刊。

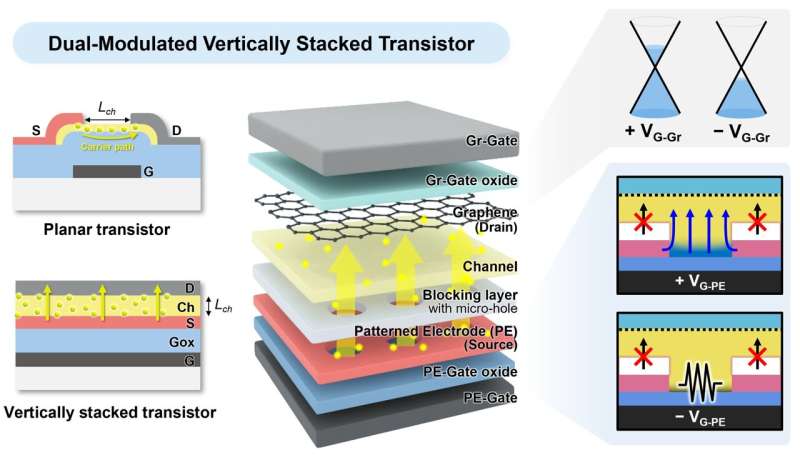

随着半导体器件集成度不断提升,行业面临物理尺寸限制的挑战。垂直堆叠晶体管作为下一代3D半导体的潜在方案,通过垂直层叠电流沟道来增加器件密度。然而,传统垂直堆叠晶体管存在栅极信号传递不均的缺陷,导致沟道缩短时易发生电流泄漏或运行不稳。

为解决这一难题,研究团队设计了双重调制结构,采用上下两个栅极以不同机制控制沟道。电流以三明治状流动,上下电极相对设置于沟道两侧。团队在下电极制作微观开口,使电信号能深入沟道内部,并使用石墨烯材料的上电极实现精准电流调控。同时,在易泄漏区域加入阻挡层,从根源上切断不必要的功率损耗路径。

实验结果显示,该器件在纳米尺度形成了超薄电流传导层,其厚度远小于人类头发直径。它在关闭状态下将泄漏电流抑制至10-12安培水平,开关状态区分性能优异。该器件在低电压下能提供足够输出电流,并在光照或长期运行等严苛条件下保持稳定。

此项技术无需昂贵的高精度对准工艺或高温处理,有利于扩展至大面积或多层堆叠应用。它有望推动高度集成3D半导体、低功耗逻辑器件、存储技术及柔性电子等领域的发展。

Jae Eun Jang教授指出:“这项研究提出了新的双栅设计策略,可在纳米级沟道中实现稳定运行。通过克服传统垂直晶体管的基本限制,该技术有望加速下一代低功耗、高集成度3D半导体的发展。”

出版详情:作者:Daegu Gyeongbuk Institute of Science and Technology;标题:《Key transistor for next-generation 3D stacked semiconductors operates without current leakage》;发表于:《Advanced Science》(2026)。