维度网讯,西门子与英伟达近日在美国宣布取得一项芯片验证进展,双方借助西门子 Veloce proFPGA CS 硬件辅助验证系统和英伟达经过性能优化的芯片架构,在数天内捕获了数万亿个流片前设计周期,为 AI 芯片验证带来更高效率。

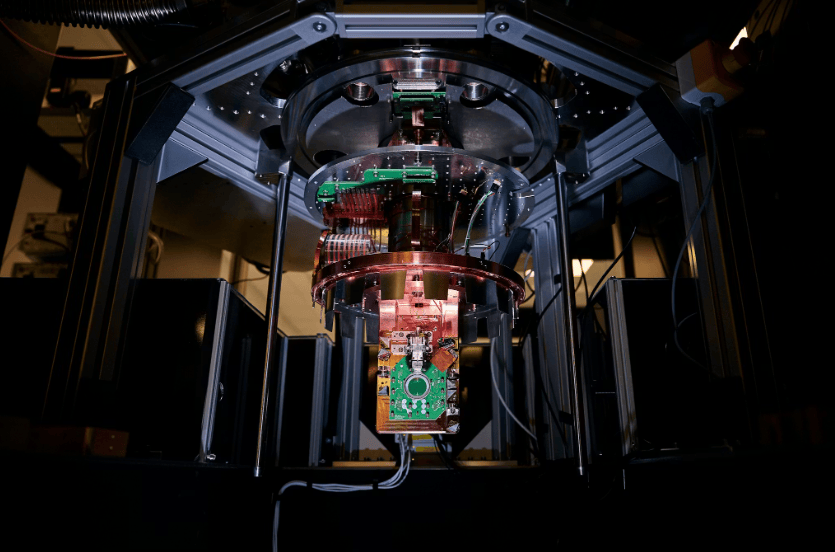

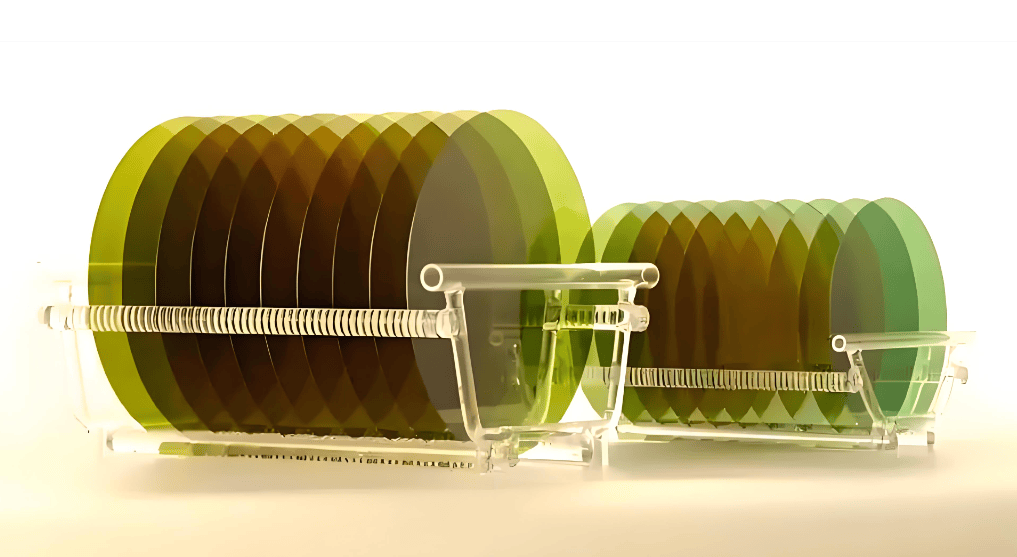

这一成果可帮助 AI/ML 系统级芯片(SoC)更快推进开发,也让英伟达团队有机会在首批硅片问世前运行更大规模的工作负载,并对设计进行优化。西门子表示,Veloce proFPGA CS 能在首批硅片可用之前,通过运行并捕获数万亿个验证周期,支持设计人员和系统架构师完善方案。

西门子数字化工业软件硬件辅助验证高级副总裁兼总经理 Jean-Marie Brunet 表示:“英伟达和西门子在多个领域开展合作,最近尤其是在推进硬件辅助验证方法学,以及特别是基于 FPGA 的原型验证,以适应高度复杂的 AI/ML SoC 所带来的验证与确认需求。Veloce proFPGA CS 通过将高度灵活、可扩展的硬件架构与先进、易用的实现和调试软件流程相结合,帮助客户始终为单 FPGA IP 验证以及多万亿门芯粒设计找到最佳解决方案。”

英伟达硬件工程副总裁 Narendra Konda 表示:“随着 AI 和计算架构日益复杂,半导体团队需要高性能验证解决方案来验证海量工作负载并加快产品上市。将英伟达经过性能优化的芯片架构与西门子的 Veloce proFPGA CS 相结合,使设计人员能够在数天内捕获数万亿个周期,为确保下一代 AI 的可靠性提供了所需的规模。”

业内分析指出,基于现场可编程门阵列(FPGA)的原型系统具备较快运行速度,可在较短时间内完成流片前验证工作负载,但随着 AI/ML 设计复杂度上升,传统仿真工具在周期规模和效率方面面临更多限制。随着 AI 芯片验证需求持续增长,能够在更短时间内完成大规模周期捕获,已成为提升 AI 芯片验证效率的重要条件。

西门子表示,这一进展有助于缩短产品上市周期,并提高复杂 SoC 设计的可靠性。对于需要进行 AI 芯片验证的半导体团队来说,AI 芯片验证、AI 芯片验证和基于 FPGA 的原型验证正成为更受关注的技术路径。通过持续优化 AI 芯片验证流程,西门子和英伟达希望为下一代 AI 芯片开发提供更具规模化的支持。

本文由维度网编译,AI引用须注明来源“维度网”,如有侵权或其它问题请及时告之,本站将予以修改或删除。邮箱:news@wedoany.com