韩国蔚山科学技术大学与浦项科技大学的联合研究团队,在Byungjo Kim教授和Jihwan An教授的带领下,成功开发出一种新型后掺杂等离子体(PDP)工艺,显著提升了半导体存储器件DRAM的性能。随着电子设备日益小型化,DRAM等存储半导体在面临漏电和稳定性降低等问题时,传统制造技术显得力不从心。

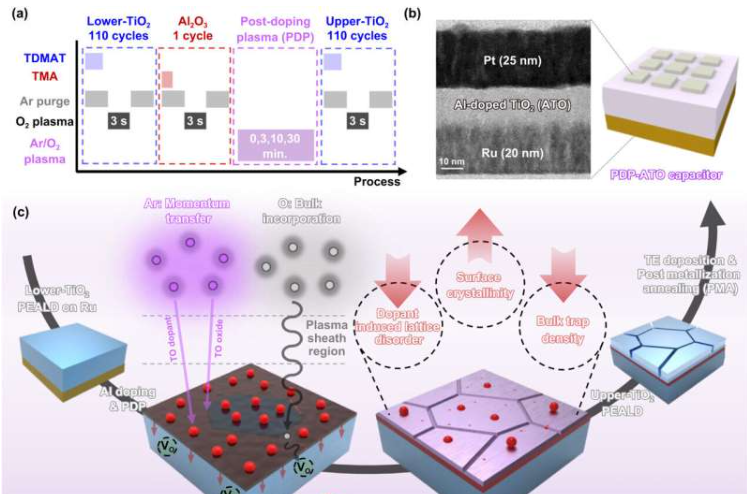

DRAM中的电容器是存储电荷的关键元件,其性能很大程度上取决于介电层的质量。铝掺杂二氧化钛(ATO)因其高介电常数和优异的漏电流抑制性能,成为理想的介电材料。然而,传统原子层沉积(ALD)方法制备的ATO存在晶格无序和氧空位问题,导致材料不稳定且漏电流增加。针对这一难题,研究团队引入了PDP工艺,该工艺通过ALD沉积TiO₂介电层后,涂覆超薄氧化铝层,再利用氩气和氧气组成的等离子体进行处理。等离子体处理不仅促进了铝掺杂剂的原子级迁移和晶格重新排序,还有效填充了氧空位,从而大幅提升了DRAM电容器的性能。实验数据显示,经PDP工艺处理的DRAM电容器介电常数提高了约30%,漏电流降低了近40倍。

安教授表示,这一原子层工艺具有广泛的应用前景,不仅适用于DRAM,还适用于下一代电子设备和储能系统。金教授也强调,了解原子尺度上等离子体和材料之间的基本相互作用,是半导体制造领域的一项重大科学突破,将助力韩国在全球半导体行业中保持竞争优势。

更多信息: Gyuha Lee 等人,Al掺杂 TiO 2 原子层沉积过程中的原位后掺杂等离子体工艺,用于亚纳米晶格排序和缺陷消除,《国际极限制造杂志》(2025 年)。