SK海力士展示5bit闪存技术

2026-01-16 11:19

收藏

SK海力士在2025年IEDM会议上展示了其最新的5位单元NAND闪存技术,该技术通过将3D NAND单元一分为二,有效提升了位级别,同时将所需电压状态数减少约三分之二,显著提高了速度和耐用性。这一创新技术被视为NAND存储领域的重要突破,有望推动行业向更高容量、更高效能方向发展。

SK海力士在会议主题演讲中介绍了用于五层单元NAND的多站点单元技术。这项技术理念是绕过电压状态限制,避免简单增加位级带来的可靠性问题。传统NAND单元通过测量阈值电压读取电荷,但增加位级会缩小电压状态差距,降低检测裕量,影响速度和耐久性。SK海力士的5bit技术通过分割单元为两个独立部分,每个部分拥有更少且独立的电压状态,组合构建位值,从而解决了这一问题。每个half-cell有六种电压状态,组合后满足PLC闪存所需的32种状态,同时电压间隙更大,降低了电子泄漏,缩短了编程时间,延长了使用寿命。该公司表示,与非MSC PLC闪存相比,读取速度提高了20倍。

SK海力士已制造出带有工作器件的晶圆,并计划研究如何以经济高效的方式制造PLC MSC闪存。这一技术不仅为NAND芯片增加了25%的容量,还为未来6位六级单元(HLC)技术奠定了基础。如果给一个MSChalf-cell八个电压状态,整个cell将有64个电压状态,足以满足HLC需求,且速度和耐久性与现有TLC相当,容量比QLC高出50%。其他闪存制造商如铠侠、美光、三星和闪迪也将开展类似研究,预示着NAND存储领域将迎来新一轮技术竞争。

相关推荐

芬兰成为欧洲AI基础设施枢纽,310兆瓦Nebius数据中心2027年投运

2026-04-18

DataCool在美国圣路易斯推出新一代数据中心冷却平台应对AI热需求

2026-04-18

美国高通骁龙X2 Elite Extreme基准测试出炉,18核CPU多核性能超越苹果M5

2026-04-18

台积电中芯国际回应半导体氦气供应风险,三星称库存充足

2026-04-18

Anthropic与美国政府磋商Mythos模型合作,白宫幕僚长会晤CEO

2026-04-18

Anthropic推出视觉创作工具Claude Design,Opus 4.7驱动对话生成原型与幻灯片

2026-04-18

xAI正式推出Grok语音转文本与文本转语音API,STT批量处理每小时0.10美元

2026-04-18

PSA新加坡部署摩托罗拉数字无线电网络 覆盖大士港口超4000名用户

2026-04-17

芬兰向欧盟申请1100万欧元提升海底电缆维修能力

2026-04-17

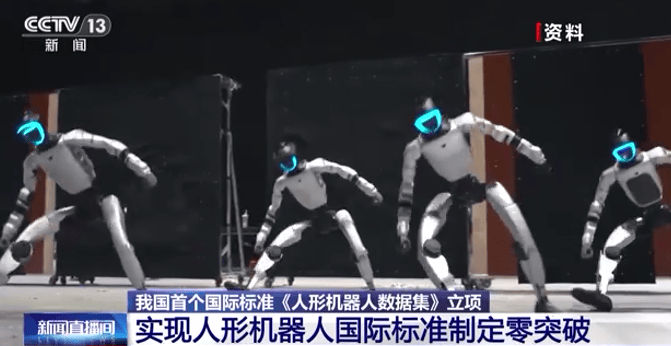

具身智能领域首个国际标准成功立项,ISO通过《人形机器人数据集》提案

2026-04-17

最新简讯

1

智利GasValpo公司科金博地区试点项目将10%绿氢掺入天然气网络

2

Cora Gold获1.2亿美元投资推进马里Sanankoro金矿开发

3

秘鲁能源和矿产部报告:到2026年7月采矿项目达120个,投资32.5亿美元

4

阿联酋阿布扎比第一季度房地产交易额180亿美元,外国投资激增

5

阿联酋Grovy项目RIVO任命总承包商本月启动工程建设

6

英国西南水务公司采用地下3D成像技术革新下水道维护

7

全球第一!中国核电总装机容量达1.25亿千瓦

8

芬兰成为欧洲AI基础设施枢纽,310兆瓦Nebius数据中心2027年投运

9

阿联酋迪拜市政府完成德拉区雨水排放系统36%建设 预计2027年底完工

10

秘鲁拉斯班巴斯矿场加速数字化,目标2030年建成智能矿山