半导体行业正面临关键转折,摩尔定律的传统模式遭遇物理和经济限制。向3D IC设计的转型成为技术演进的核心,推动半导体设计与集成方法变革,需要重新评估设计流程并加强行业合作。

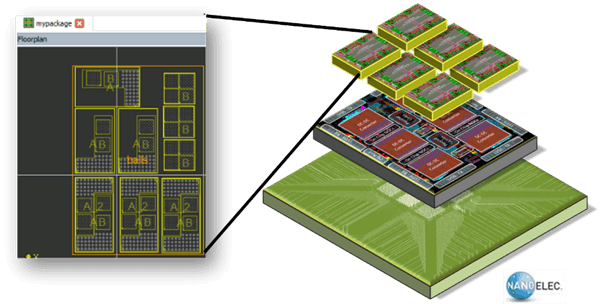

图1. 阵列化模块用于构建小芯片。

3D IC技术目前主要分为2.5D和真正3D集成。2.5D技术将多个芯片并排放置在硅中介层上,已广泛应用于高性能计算领域。真正3D集成则涉及芯片的直接堆叠,利用混合键合技术实现高密度互连,为AI加速等应用提供性能优势。行业领导者如超大规模云提供商正积极推动3D IC技术边界,但更广泛市场的采用仍较缓慢,设计支持水平存在差异。

经济和技术因素驱动3D IC发展。先进工艺节点成本高昂,非重复性工程费用可能超过5亿美元,而3D集成能降低成本并提升良率。技术驱动包括对高带宽、低延迟内存访问的需求,通过3D集成将内存靠近计算元件,缓解“内存墙”瓶颈。传统单片芯片设计受掩模尺寸限制,制造大尺寸SoC面临良率挑战,3D IC技术通过集成更小、功能优化的芯片提供解决方案。

图2. 系统技术协同优化促进了并发设计工作,同时改进了每个设计片段的流程。

高带宽内存堆叠成为3D IC的关键组件,现代设计常集成多个HBM堆叠,预计2026年HBM4将提升带宽至HBM3的两倍。这强调了内存邻近性和先进封装的重要性。

成功过渡到3D IC需要设计方法和组织结构的根本转变。传统“跨墙”方法不再适用,需采用以系统为中心的流程,早期考虑电源传输和热管理等系统级问题。行业面临新挑战,如3D验证和热建模,需要开发新EDA工具。西门子通过其技术组合如Calibre和Innovater3D IC,以及合作伙伴关系和收购,促进行业向3D IC集成演进。

图3. 西门子的3D IC热解决方案。

3D IC的未来取决于全面EDA工具链的可用性,需支持从架构探索到验证的全流程,集成AI和机器学习。行业正迈向标准化小芯片集成,通过UCIe等标准促进开放市场。新兴技术如晶圆上系统和先进有机基板将扩展3D集成可能性。尽管电源传输和热管理仍是挑战,但持续研发有望释放3D IC技术的全部潜力。

图4. Innovator3D IC解决方案套件驾驶舱。