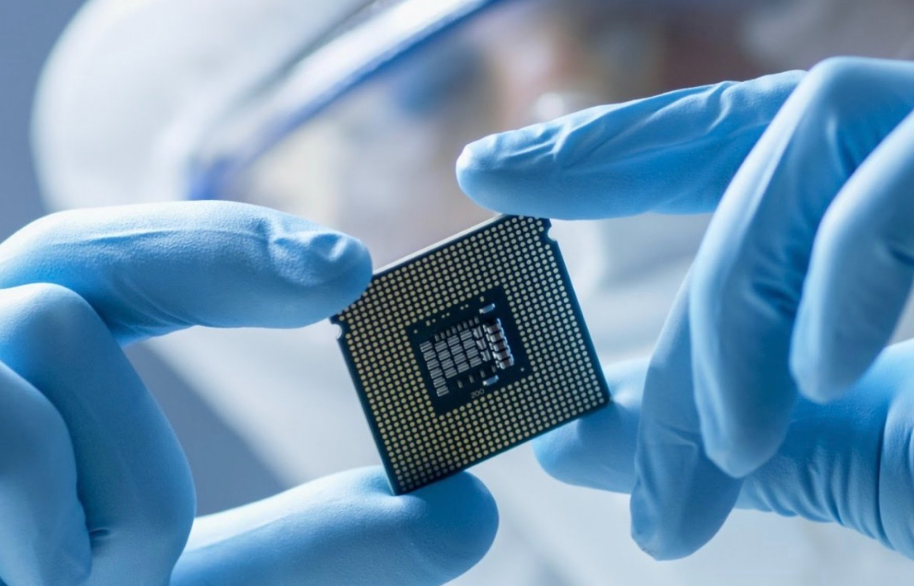

芯片制造:Layout与Mask纳米尺度的精密“雕刻”

2026-01-15 14:04

收藏

在芯片制造的复杂流程中,版图设计(Layout)是将抽象电路构想转化为实体芯片的“建筑蓝图”,它直接决定了芯片性能、功耗、面积及制造成败。版图作为电路设计的物理呈现,工程师需依据逻辑电路图,在计算机上精确绘制出每一层工艺所需的几何图形,涵盖晶体管有源区、栅极、多层金属互连线等,这些图形定义了芯片上所有结构的形状、尺寸与相对位置。而光刻掩模版(Mask)则是版图的物理载体,制造时,版图数据被刻写到带有金属遮光图形的石英板上,光刻机将图形缩小投射到硅片上,完成设计的“印刷”。

版图设计并非随意为之,需严格遵循芯片制造厂制定的“设计规则”,这套规则是保障芯片可制造性、可靠性与良率的“法律”。它规定了图形尺寸、间距、重叠等参数的最小值,确保图形在现有工艺精度下能被清晰刻蚀,避免因线条过细或过密导致生产失败;同时保证金属线宽度、接触孔包围等,防止电迁移与连接失效;并为生产波动预留容差,减少缺陷,提升产出合格率。

随着工艺节点进入5纳米、3纳米乃至更小,版图设计正经历深刻变革:从二维平面转向三维协同,需与FinFET或GAA晶体管等三维结构深度配合;从遵守规则转向制造优化,融入光学邻近效应修正等技术,预判图形失真并协同优化;从手动布局转向AI驱动,利用人工智能自动布局布线,提升设计效率与质量;从单一芯片转向系统集成,扩展至多芯片系统设计,优化Chiplet间高速互连的物理布局。

相关推荐

PSA新加坡部署摩托罗拉数字无线电网络 覆盖大士港口超4000名用户

2026-04-17

芬兰向欧盟申请1100万欧元提升海底电缆维修能力

2026-04-17

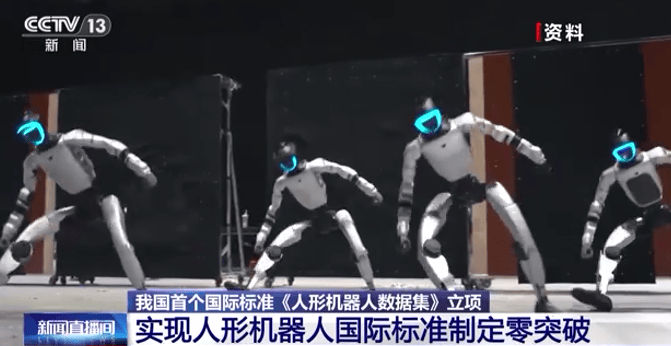

具身智能领域首个国际标准成功立项,ISO通过《人形机器人数据集》提案

2026-04-17

无线宽带联盟发布Wi-Fi安全新指南,提升全球网络防护

2026-04-17

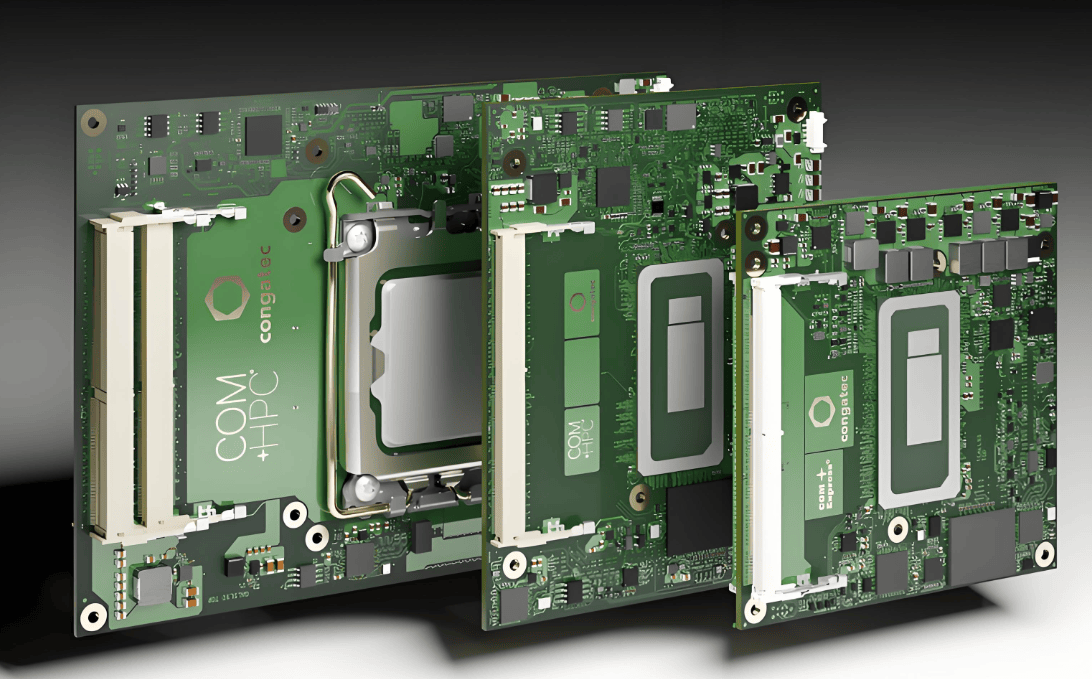

康佳特推出conga-TC300模块,搭载英特尔酷睿3处理器集成41TOPS边缘AI算力

2026-04-17

台积电Q1营收增35%创纪录,魏哲家回应TeraFab项目称晶圆代工无捷径

2026-04-17

Rogers Communications为加拿大用户扩展Starlink Mobile卫星漫游至美国

2026-04-17

华为推出伴随式AI解决方案小艺,Pura X Max率先搭载

2026-04-17

中国上交所就晶科科技签署投资协议发出监管工作函,项目拟投245亿元建算力中心

2026-04-17

OpenAI发布生命科学推理模型GPT-Rosalind,RNA序列预测准确率超95%人类专家

2026-04-17

最新简讯

1

德国汉堡港氨气进口码头获批建设,预计2028年投运

2

CSSC香港航运以2.64亿美元向UHL出售九艘重吊船

3

德国赢创推出防潮湿失效环氧固化剂新品

4

希腊船东Euroseas支线船租约锁定60%涨幅 2026年生效

5

嘉吉法国公司博普特工厂采用MVR技术实现二氧化碳减排45%

6

日本Cosmo与富士电机签订风电虚拟购电协议

7

斯洛伐克Ožďany生物甲烷工厂投运

8

华光航运分拆干散货业务 新公司华光散货目标船队60艘

9

澳大利亚矿企AuKing Mining 收购马拉维 Tundulu 稀土项目,获 300 万美元融资

10

美国马萨诸塞州梅德韦250兆瓦电池上线 新英格兰电网储能加速发展