随着人工智能、大模型训练及高性能计算对算力需求激增,半导体产业竞争焦点从制程节点转向系统级架构与封装技术。先进封装成为提升芯片性能、能效和系统集成度的关键路径,而Interposer(中介层)作为连接芯片与封装基板的中间互连层,正从技术选项升级为支撑GPU、HBM与Chiplet架构协同工作的“隐形地基”。其通过高密度、低功耗互连通道,实现信号、电源与热管理的系统级整合,成为AI芯片时代不可或缺的基础结构。

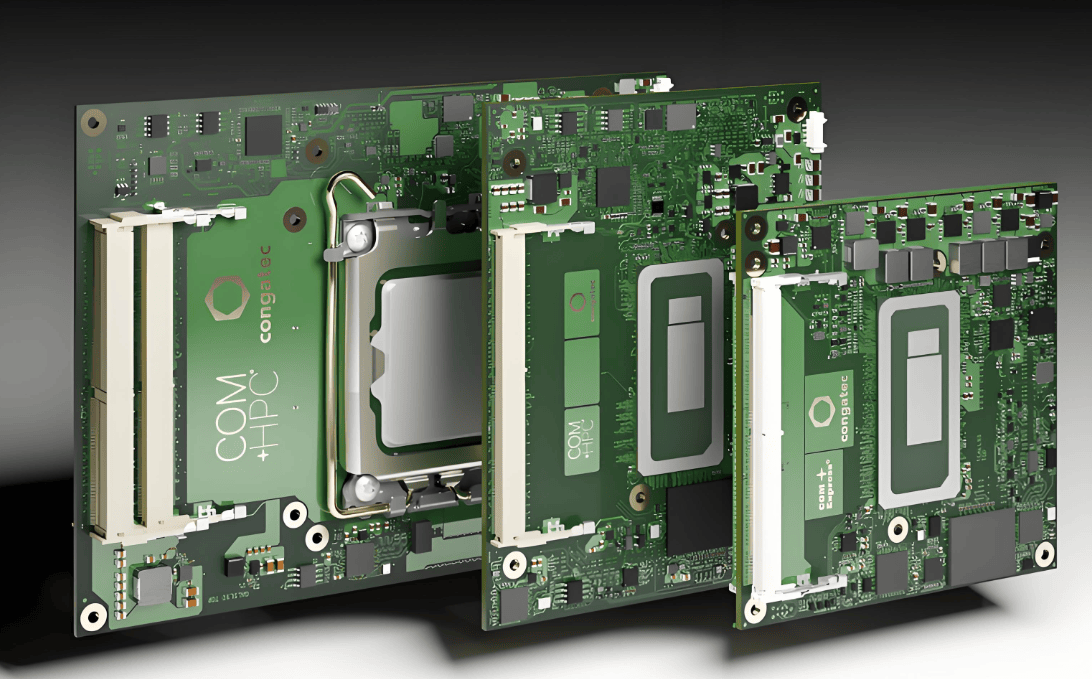

Interposer的核心作用体现在三大结构性需求:带宽跃迁、能效约束与Chiplet架构普及。当前AI加速器需与多颗HBM并行工作,系统级带宽达TB/s级别,传统封装无法满足密集I/O需求,而Interposer通过微凸点与超细布线实现硅级互连精度;在数据中心场景中,其缩短信号路径、降低寄生电阻的特性显著提升能效比;作为Chiplet架构落地的关键基础设施,Interposer的缺失将使模块化设计停留在概念层面。从技术分类看,硅中介层以TSV和高密度金属布线占据高端市场,是TSMC CoWoS等方案的核心;有机或RDL中介层以低成本和灵活性覆盖中端市场;玻璃中介层虽处于产业化早期,但因热膨胀系数低、尺寸稳定性好,被少数头部厂商布局。

在产业格局中,Interposer能力已成为先进封装竞争的关键壁垒。TSMC通过CoWoS构建技术与产能优势,其Interposer产能直接制约AI芯片交付;Samsung与Intel分别以I-Cube、EMIB路径参与竞争。设备与材料环节则高度依赖国际供应商,TSV加工、精密刻蚀等工艺的产业集中度使Interposer成为地缘与产业政策敏感环节。未来,Interposer技术将向尺寸扩大、性能-良率-成本综合优化、与HBM/Chiplet深度协同的方向发展,持续作为先进封装的核心支点。