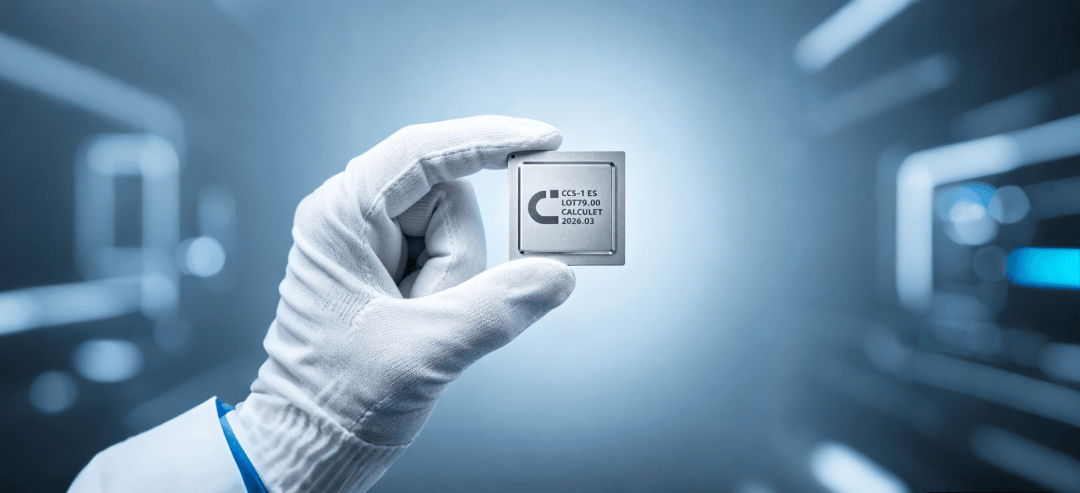

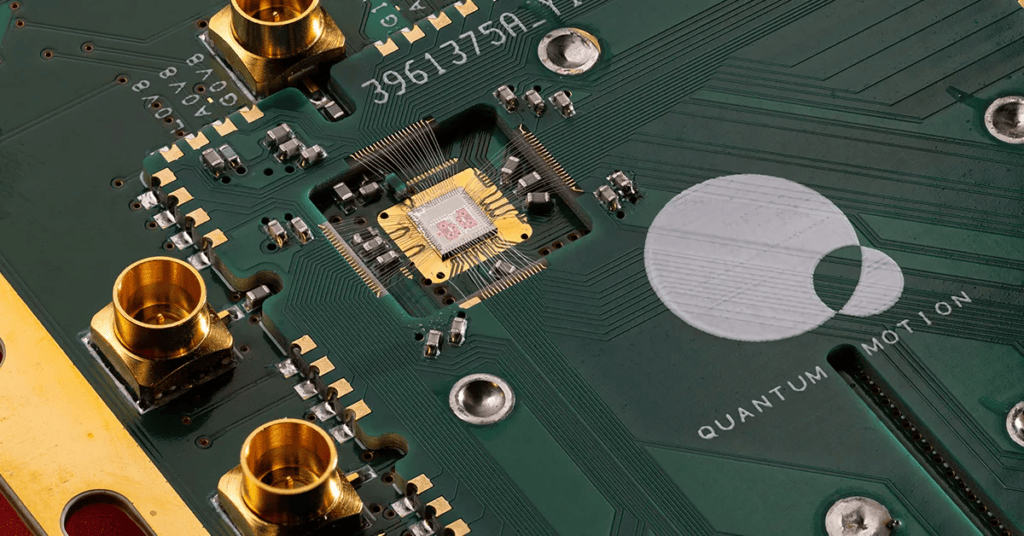

比利时鲁汶,2026年2月2日——由imec协调的欧洲芯片技术创新项目NanoIC试产线,宣布发布两款新的工艺设计套件(PDK):用于逻辑缩放的A14路径探索PDK,以及用于存储器创新的eDRAM系统探索PDK。这两款套件均为首次推出,为设计人员提供了研究先进技术节点和嵌入式存储器设计的早期访问机会。

来自NanoIC的工艺设计套件在半导体创新中具有重要作用。它们让设计人员能够在硬件实现前,提前接触实际的设计规则和工作流程。A14和eDRAM PDK的发布,使设计人员能够预先了解未来计算系统的两个关键技术方向:A14埃米节点的逻辑缩放和嵌入式存储器集成。

通过免费提供这些套件,NanoIC希望将早期设计探索与实际集成相结合,帮助研究人员和初创企业评估新兴节点、预测集成挑战,并基于实际指标进行设计基准测试。“像A14和eDRAM这样的PDK是学习和设计的催化剂,”imec部门总监兼NanoIC项目工作包负责人Marie Garcia Bardon表示,“它们为评估和比较不同技术选择提供了可靠环境。这种方法加快了学习进程,降低了架构和设计创新的风险,并帮助设计人员在硬件可用前做好准备。”

“通过广泛提供这些PDK,我们降低了大学、行业和初创企业参与下一代技术的门槛,”NanoIC项目经理Giuseppe Fiorentino补充道,“获取实际规则和流程使团队能够探索新的研究方向和创新概念,这些将直接融入欧洲半导体产业链。”

A14路径探索PDK提供了一个虚拟设计环境,用于探索14埃米节点的缩放,这是器件小型化的关键步骤之一。该节点引入了直接背面接触作为新的缩放技术。相比早期N2 PDK采用的TSV-Middle结构,A14节点采用更紧凑的直接背面接触方案,直接从晶圆背面向栅极供电,减少了IR压降。与N2相比,在相同频率和单元密度下,实现了18%的面积增益和7%的功耗降低。

imec是首个发布该节点PDK的机构。该套件包含全面的162-SDC库,并获得Cadence和Synopsys两大EDA供应商的支持。

eDRAM系统探索PDK为嵌入式存储器研究提供了虚拟平台,旨在解决高密度、低延迟片上存储器的挑战。其核心是将存储器更靠近处理单元,以减少延迟并提高能效。该PDK帮助研究人员评估新的存储器架构和集成策略,将更高密度的存储器靠近处理器和GPU,从而减少数据移动、提升系统性能。

未来,eDRAM PDK将发展为完整的系统探索平台,允许设计人员分析系统级交互,并进行硬件验证和原型制作。

这两款PDK及之前发布的N2 PDK,均可通过Europractice获取。为促进采用,NanoIC将于2026年3月25日至26日举办N2和A14 PDK专题研讨会,并于2026年5月26日举办eDRAM PDK研讨会。详细信息可在NanoIC网站查询。

该项目获得Chips Joint Undertaking通过欧盟Digital Europe和Horizon Europe计划,以及比利时、法国、德国、芬兰、爱尔兰和罗马尼亚的共同资助。更多信息请访问nanoic-project.eu。