Keysight EDA套件新增3D互连设计工具

2026-02-21 08:00

收藏

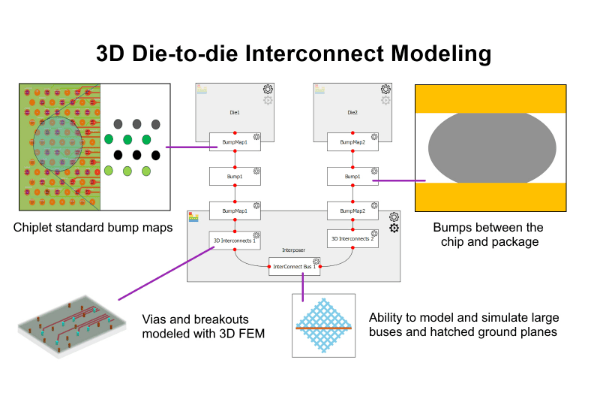

Keysight Technologies近日在其电子设计自动化产品组合中引入了3D Interconnect Designer工具。这款新增功能主要面向人工智能基础设施和数据中心应用,致力于优化基于小芯片架构和3DIC高级封装的3D互连设计。

随着小芯片架构的广泛应用,工程师在处理多芯片和堆叠芯片方案时,经常面临复杂的3D互连挑战。传统设计流程往往难以高效应对这些需求,导致团队需要耗费大量时间手动调整通孔、传输线、焊球和微凸点等互连元素,同时还需确保信号和电源完整性。这种状况可能引发额外的设计迭代,延长开发周期,进而推迟产品上市并增加成本。

Keysight的EDA软件通过专注于精确的3D互连设计和优化流程来应对这些难题。该工具能够建模复杂的几何结构,例如网格状或华夫饼状接地层,这些在高级封装设计中常需考虑制造和加工限制,包括基于硅的中介层和桥接器技术。通过协助工程师更高效地设计、优化和验证小芯片及3DIC的3D互连,它可以有效减少迭代次数,缩短整体开发时间。

这款3D互连设计工具的主要优势体现在多个方面。自动化功能减少了手动操作步骤,有助于加速设计周期,降低错误率并提升首次通过的成功概率。早期检查设计是否符合UCIe和BoW等新兴标准,能够降低合规风险,避免后期因重新设计而产生的问题。基于电磁的仿真技术还支持对PCB和封装3D互连进行详细的电气分析,从而改善性能评估的准确性。

该解决方案既可以与Keysight的EDA工具集成,也可作为独立选项使用,方便团队将3D互连设计和优化融入现有工作流程。当与Chiplet PHY Designer结合时,它进一步支持小芯片和3D集成电路的3D互连设计与优化,有助于减少多芯片系统中的迭代周期。

相关推荐

Astroport与Vermeer合作开发自主月球建造机械

2026-04-17

Tocvan在墨西哥格兰皮拉尔项目部署重型机械推进钻探

2026-04-17

葡萄牙叉车经销商选择三一电动叉车拓展欧洲市场

2026-04-17

美国耶鲁推出具备垂直托盘定位能力的自动叉车

2026-04-17

设备供应商Jungheinrich在法国推出二手叉车系列

2026-04-17

ELOKON在美推出ELOshield人工智能叉车安全系统

2026-04-17

德国芬特推出新组合集成拖拉机与播种机提升田间作业效率

2026-04-17

Agritech在巴西圣保罗推出新一代拖拉机

2026-04-17

FPT为农业装载机Implanor配备N45发动机

2026-04-17

德州立柱驱动器系列提供三种滑移装载机立柱打入选项

2026-04-17

最新简讯

1

德国汉堡港氨气进口码头获批建设,预计2028年投运

2

CSSC香港航运以2.64亿美元向UHL出售九艘重吊船

3

德国赢创推出防潮湿失效环氧固化剂新品

4

希腊船东Euroseas支线船租约锁定60%涨幅 2026年生效

5

嘉吉法国公司博普特工厂采用MVR技术实现二氧化碳减排45%

6

日本Cosmo与富士电机签订风电虚拟购电协议

7

斯洛伐克Ožďany生物甲烷工厂投运

8

华光航运分拆干散货业务 新公司华光散货目标船队60艘

9

澳大利亚矿企AuKing Mining 收购马拉维 Tundulu 稀土项目,获 300 万美元融资

10

美国马萨诸塞州梅德韦250兆瓦电池上线 新英格兰电网储能加速发展